FPGAを用いたAES暗号化装置の試作

1. 緒言

近年、情報保護の重要性が高まったことを受けて、通信データを暗号化する需要が高まりつつある。 本研究では、Ethernetで利用できる「通信データ暗号化装置」の試作を目標として、FPGAボード上にAES暗号化回路の試作を行なった。

2. AES(Advanced Encryption Standard)とは

AESは、米国政府によって選定された次世代標準暗号化方式である。

AESとして採用されたRijndaelはベルギーの数学者によって開発された秘密鍵暗号化である。

この暗号は、鍵とデータをそれぞれブロックとして分割して暗号化する方式で、

鍵とブロック長は128bit、192bit、256bitが規定されている。

AES方式での暗号化は、次の4つの操作を10回(暗号強度128bit時)繰り返すことで行われる。

SubBytes、ShiftRows、MixColumns、AddRoundKey

AESでは1byteのブロックを基本として暗号化を行っており、暗号化前と後でデータのサイズが一致するという特徴を持つ。

最終ラウンド(10回目)では、SubBytes、ShiftRows、 AddRoundKeyのみを行い、暗号化処理が完了する。

AESについては名古屋工業大学のA.I.Lab WebSiteに分かりやすい解説がある。

http://mars.elcom.nitech.ac.jp/security/aes/overview.html

3. 暗号化回路の設計

通信内容の暗号化を目標として、128bitの暗号強度、ECBモードのAES暗号化回路をFPGAに実装するための研究を進めた。 本研究ではXILINX社の評価ボード「Spartan-3E Starter Kit」を使用した。

3.1 ISE 8.2i WebPackによるVHDL回路設計

AES暗号化を行う回路をハードウェアとして実装するために、VHDLを用いて図1に示す4つの処理、 および処理回路同士を接続するインターフェース部の回路設計を行った。回路の規模を小さく抑える為に 入出力インターフェース部に必要なbit数を削減し、暗号キーを内部保持するなどの改良を行った。 その結果、FPGAに構成可能な規模の暗号化回路を構築することができた。

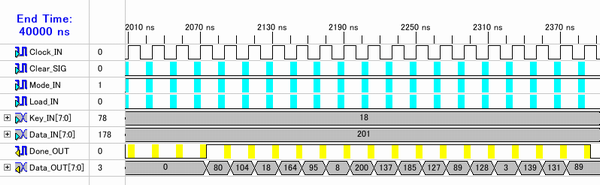

3.2 ISE Simulatorによる回路の検証

AES暗号化回路が正しく構成されているかを検証するために、ISE Simulatorに検証データを入力して動作を確認した。 128bitの入力を10パターン試した結果、AES検証データとの一致が確認できた。

4. 結言

暗号強度128bitのAES暗号化回路をSpartan-3E FPGA内に構築することができた。

また、シミュレーション結果より、50MHzのクロック動作時において最大約50Mbpsの速度で

暗号化・復号化処理を行えることが確認できた。

ただし、今回構築できたのはAES暗号化部分のみであり、Ethernetを含めた外部インターフェース部分が未完成のため、

この開発が今後の課題である。