VHDLを用いたマイクロプロセッサCOMETIIの設計および試作

1.緒言

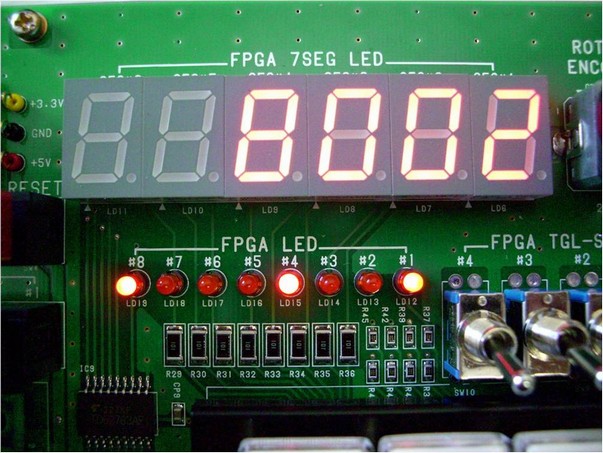

近年の半導体産業技術は、飛躍的な進歩を遂げ、ハードウェアの開発環境や設計手法も急激に変化している。 ディジタル回路設計も、HDLを用いた方法が主流となり、FPGAやCPLD上に設計した回路を自由に構成できるようになった。 本研究では、情報処理技術者試験で出題されている仮想マイクロプロセッサCOMETIIをVHDLで設計した。 VHDLソースコードをAltera社のQuartusII Web Edition Version 6.1を用いてコンパイルし、 Altera社製ACEX1KファミリEP1K30TC144-2搭載のFPGAボード上に構築し、動作させることを行った。

2.COMETIIの仕様、アーキテクチャ

COMETIIの仕様は情報処理技術者試験センターで公開されているので、URLを載せる。 →情報処理技術者試験センター http://www.jitec.jp/

3.COMETII評価

COMETIIの動作確認のため、シミュレーションを行い、その後、CASLIIの命令を用いて動作チェックプログラムを記述し、 ハンドアセンブルした機械語命令を実行した。表3にCASLII命令の内、LD、LAD、ADDA、ST、RETを用いた動作チェック用プログラムを示す。

|

START LD GR1,Data LAD GR2,0003h ADDA GR1,GR2 ST GR1,Result END RET Data 7FFFh Result 0000h |

#0000: 1010 000A #0002: 1220 0003 #0004: 2412 #0005: 1110 0100 #0007: 8100 #000A: 7FFF #0100: 0000 |

|---|

このプログラムは、COMETIIに実行アドレス#000Aの内容をGR1にロードし、GR2に#0003を転送し、

その2つを算術加算し、その結果を実行アドレス#0100に格納することを行っている。

動作確認実験では、すべての命令について実行し、正確に動作することを検証した。

ただし、本研究ではSVC命令のみ実装していないため、SVC命令の動作チェックはしていない。

4.結言

VHDLを用い、COMETを改良することによってマイクロプロセッサCOMETIIを設計し、FPGA (EP1K30TC144-2)上に実装した。 COMETII上で機械語プログラムを実行させた結果、SVC命令を除く全機械語命令が確実に動作していることを確認できた。